## Self-Compensation of DC-DC Converters Under Peak Current Mode Control

A. El Aroudi, K. Mandal, D. Giaouris and S. Banerjee

A new self-compensation technique is proposed for eliminating subharmonic oscillation and chaotic regimes in dc-dc switching converters under peak current mode control. The proposed method extracts a control signal from the error between the inductor current and a suitable reference and does not require an external signal generator as in the conventional ramp compensation scheme. We have obtained the analytical expressions of the control domain using Filippov method. Simulation results show that the proposed technique can be implemented using standard analog devices and can effectively eliminate subharmonic and chaotic oscillations and can ensure a stable operation for a wide range of the duty ratio.

Introduction: Subharmonic and chaotic oscillations are phenomena that commonly occur in dc-dc switching converters and their control is of great importance for power electronic designers. Although many control techniques exist in the literature for suppressing these undesired behaviors, slope compensation using an external periodic ramp signal with a constant slope is the conventional strategy preferred by engineers for stabilizing switching converters under peak current mode control [1, ch.11]. The use of constant slope compensation can increase the stability range of the desired periodic behavior, but as a penalty, it reduces some of the benefits of current mode control. For example, a drawback with this strategy is that the inductor current peak value deviates from its desired reference which can cause severe problems in applications where an accurate tracking of the reference signal is needed such as in power factor correction [2] and in grid-connected photovoltaic systems [3].

In order to accurately track the reference current while eliminating subharmonic oscillation in a dc-dc buck converter, a dynamic slope compensation scheme was proposed in [4]. The technique was also adapted for a boost ac-dc converter in [2]. In both these approaches an external signal generator is still needed. Another technique proposed in [5] consists of extracting the control signal from the output voltage after differentiation, integration and resetting to zero. The resulting compensation signal is practically sinusoidal with a time varying slope with an optimum value at the switching instant. However, the technique, using the output voltage for extracting the compensating signal, can only be applied to the buck converter for which the derivative of the output voltage is continuous. For other switching converters, the derivative of the output voltage is discontinuous and the previous technique will result in noise problems.

In this Letter a novel self-compensation technique is proposed for eliminating subharmonic and chaotic oscillations in all dc-dc switching converters under peak current mode control. The technique is based on extracting a control signal from the error between the inductor current and a constant reference being applicable to the converter. The novel control strategy achieves the same control effect of the existing compensation schemes with the possibility of an accurate reference tracking.

We begin our study with a brief description of the technique followed by a stability analysis and a possible realization using standard analog devices. Some design-oriented expressions are also provided for ensuring the stability of the system.  $PSIM^{\odot}$  simulations are used to validate its operation and performances.

The proposed self-compensation strategy: The inductor current in dc-dc converters includes a dc component and ac switching ripple. This Letter proposes a method to eliminate subharmonic and chaotic instabilities by utilizing the ac inductor current ripple. We propose a novel ripple-dependent self-compensating signal governed by the following expression:

$$v_{\text{mod}}(t) = \frac{r_a}{T} \int_0^{t \mod T} (i_r - i_L(\zeta)) d\zeta \tag{1}$$

where  $i_r$  is a current reference and  $r_a$  is suitable gain both to be specified later. The value of the integral variable is reset to zero at the beginning of each switching cycle of time period T.

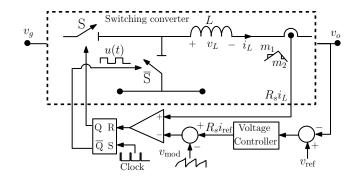

Unified dynamical model and stability analysis: Fig. 1 shows the unified three-terminal circuit diagram of elementary switching converters buck, boost and buck-boost under peak current mode control. All these

**Fig. 1** Unified circuit diagram of an elementary switching converter such as buck, boost and buck-boost under CMC. The block in dashed border can be changed depending on the converter topology chosen.

converters have a three-terminal switching cell including an active switch S and a passive switch  $\overline{S}$ . The common node between the switches S and  $\overline{S}$  connects to the inductor whose inductance is L. The switching element  $\overline{S}$  is a diode in unidirectional converters while it is a transistor in bidirectional and synchronous converters. The switch S is closed (u=1) at the beginning of each switching cycle and it opens (u=0) when the inductor current (scaled by a gain  $R_s$ ) reaches the signal  $R_si_{\rm ref}-v_{\rm mod}$ . The state of the switch  $\overline{S}$  is complementary to that of S.

For simplicity, the output voltage  $v_o$  and the reference provided by the voltage loop are considered constant. The equation governing the behavior of the inductor current is

$$\frac{\mathrm{d}i_L}{\mathrm{d}t} = m(t) = \begin{cases} m_1 & \text{for } u = 1\\ m_2 & \text{for } u = 0 \end{cases}$$

(2)

where  $m(t) = v_L/L$  and  $v_L$  is the inductor voltage. The parameters  $m_1$  and  $m_2$  are the rising and the falling slopes of the inductor current respectively. The switching condition can be expressed as follows:

$$\sigma(t) := R_s(i_{\text{ref}} - i_L(t)) - \frac{r_a}{T} \int_0^t (i_r - i_L(\zeta)) d\zeta = 0$$

(3)

where  $i_{ref}$  is the peak current reference if no compensation is used. To perform an accurate stability analysis of the system we use Floquet theory combined with Filippov method [6, 7].

Because of the reset at each clock cycle, one of the eigenvalues is zero. The expression of the nonzero eigenvalue  $\lambda$  of the system is as follows:

$$\lambda = 1 + \frac{(m_2 - m_1)(R_s - r_a D)}{R_s m_1 + \frac{r_a}{T} (i_r - i_L(DT))}$$

(4)

The value of the effective peak current  $i_L(DT)$  can be derived by solving (3) which results in:

$$i_L(DT) = \frac{R_s(i_{ref} - m_1DT) - r_a(Di_r - \frac{D^2m_1T}{2})}{R_s - r_aD} + m_1DT \quad (5)$$

Two different choices for the parameter  $i_T$  are proposed resulting in the following versions of the new proposed self-compensation scheme.

First version ( $i_r=i_{\rm ref}$ ): Similar to the conventional linear ramp compensation scheme, the value of the peak current is smaller than the desired value  $i_{\rm ref}$ . Imposing  $\lambda=-1$  and  $\lambda=+1$  in (4) we can obtain respectively, the lower and the upper stability limits  $\ell_{m1}$  and  $\ell_M$  of the system in the parameter space. In terms of the control parameter  $r_a$ , the stability range is obtained as:

$$\ell_{m1} := \frac{R_s}{D} \left( 1 - \sqrt{\frac{1-D}{D}} \right) < r_a < \frac{R_s}{D} := \ell_M \tag{6}$$

**Second version**  $(i_r = i_{ref} - m_1 DT/2)$ : From (3) it can be demonstrated that  $i_L(DT)$  will be equal to the current reference  $i_{ref}$  if

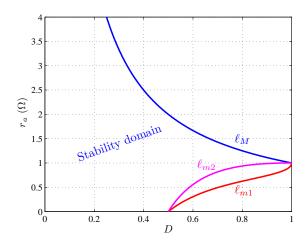

Fig. 2. Control domain in the parameter space  $(D, r_a)$

$i_r = i_{ref} - m_1 DT/2$ . In this case, the stability limits become:

$$\ell_{m2} := \frac{R_s}{D^2} (2D - 1) < r_a < \frac{R_s}{D} := \ell_M \tag{7}$$

In both versions, a value of  $r_a=R_s$  guarantees stability for all values of the duty ratio. The control domain for both cases is shown in Fig. 2 in terms of the operating duty ratio and the parameter  $r_a$  for  $R_s=1$   $\Omega$ .

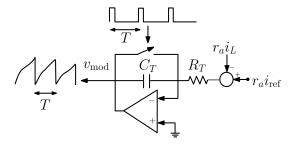

Time-domain simulation and validation of the self-compensation scheme: Numerical simulations are performed using PSIM© software to validate the theoretical results related to the novel self-compensation scheme which can be implemented by the analog circuit diagram depicted in Fig. 3 where a resettable integrator has been used. Without loss of generality, the resistance  $R_T$  and the capacitance  $C_T$  are selected in such a way that  $R_TC_T=T$ , where T is the switching period. A boost converter under peak current mode control is used to validate the proposed scheme and the related theoretical results with the following parameter values:  $v_g=5$  V,  $v_o=20$  V (D=0.75), L=1 mH, T=40  $\mu s$ ,  $i_{\rm ref}=1$  A and  $R_s=1$   $\Omega$ .

Fig. 3. Circuit diagram of the novel modulating signal generator.

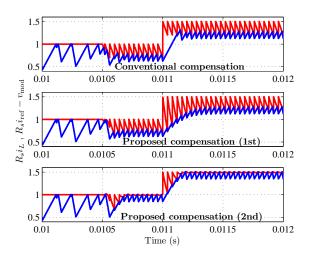

Fig. 4 shows the time domain response of a boost converter under peak current mode control. The system is operated with a duty cycle D=0.75 which implies subharmonic oscillation without compensation. At t=0.0105 s, the self-compensation strategy is applied with  $r_a=1~\Omega$  and the system is stabilized within a few switching cycles. At t=0.011 s, a step change from 1 A to 1.5 A is applied to the reference current. For a fair comparison, the amplitude of the conventional compensation ramp is selected to be equal to the one corresponding to the first version of the proposed self-compensation scheme in steady-state. This amplitude is 0.3 V. While a similar stabilizing effect can be observed in the conventional ramp compensation strategy and in the first version of the proposed self-compensation scheme, it can be noted that the second version of the proposed control technique outperforms both of them in terms of accurate current reference tracking.

Conclusions: We have presented a self-compensation technique for eliminating subharmonic and chaotic oscillations in current-mode controlled switching converters. Simulation results show that the technique can easily be implemented with a simple analog circuit. Compared with the conventional slope compensation, the strategy does not require an external signal generation and extracts a modulating signal directly from

**Fig. 4** The system response under the activation of compensation at t = 0.0105 s and to a step change in the reference current at time t = 0.011 s for the conventional linear ramp compensation scheme (top), the first version of the proposed self-compensation strategy (middle) and its second version (bottom).

the error between the inductor current and a suitable reference. The proposed strategy has the same stabilizing effect as the conventional slope compensation technique, but also has the advantage of accurate current reference tracking.

Acknowledgment: work was supported by the Spanish Ministerio de Ciencia e Innovación under grant DPI2013-47293-R.

A. El Aroudi (GAEI Research group, Departament d'Enginyeria Electrònica, Elèctrica i Automàtica, Universitat Rovira i Virgili, Barcelona, Spain) E-mail: abdelali.elaroudi@urv.cat

K. Mandal (Indian Institute of Science Education & Research - Kolkata, Mohanpur Campus, Nadia - 741246, West Bengal, India and Department of Electrical and Computer Engineering, College of Engineering, King Abdulaziz University, Jeddah, Saudi Arabia)

D. Giaouris, (School of Electrical and Electronic Engineering, Newcastle University, Newcastle upon Tyne, United Kingdom)

S. Banerjee, (Indian Institute of Science Education & Research - Kolkata, Mohanpur Campus, Nadia - 741246, West Bengal, India)

## References

- 1 Erickson, R. W. and Maksimovic, D.: 'Fundamentals of power electronics', Kluwer, Springer, 2001

- 2 Lu, W.-G., Lang, S., Zhou, L., Iu, H. H.-C. and Fernando, T.: 'Improvement of stability and power factor in PCM controlled boost PFC converter with hybrid dynamic compensation', *IEEE Transactions on Circuits and Systems I*, 2015, 62, pp. 320-328

- 3 Garcerá, G., Gonzá lez-Medina, R., Figueres, E. and Sandia, J.: 'Dynamic modeling of DC-DC converters with peak current controling double-stage photovoltaic grid-connected inverters', *Intarnational Journal of Circuit Theory and Applications*, 2012, 40, pp. 793-813

- 4 Lu, W.-G., Lang, S., Li, A. X. and Iu, H. H.-C.: 'Limit-cycle stable control of current-mode dc-dc converter with zero-perturbation dynamical compensation', *International Journal of Circuit Theory and Applications*, 2015, 43, pp. 318-328

- 5 Lu, W.-G., Jing, F., Zhou, L., Iu, H. H.-C. and Fernando, T.: 'Control of sub-harmonic oscillation in peak current mode buck converter with dynamic resonant perturbation', *International Journal of Circuit Theory and Applications*, 2015, 43, pp. 1399-1411

- 6 El Aroudi, A. Giaouris, D., Iu, H. H.-C. and Hiskens, I.: 'A review on stability analysis methods for switching mode power converters', *IEEE Journal on Emerging Topics on Circuits and Systems*, 2015, 5, pp. 302-315

- 7 Mandal, K., Chakraborty, C., Abusorrah, A., Al-Hindawi, M. M., Al-Turki, Y. and Banerjee, S.: 'Automated algorithm for stability analysis of hybrid dynamical systems', *The European Physical Journal Special Topics*, 2013, 222, pp. 757-768